# PCT-8303/8306 PCT-8360/8363

Programmer's Guide

| Document his | Document history |                                             |  |  |

|--------------|------------------|---------------------------------------------|--|--|

| date         | version          | changes                                     |  |  |

| 21.12.2015   | 12.2015          | the initial release (translated from Czech) |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

|              |                  |                                             |  |  |

#### Caution

The TEDIA® products may be used only according to the manufacturer's recommendations and precautions given in this document and other general standards and terms and may be used only such a way, that its failure caused by any reason will not be dangerous to any person or property.

#### **Disclaimer**

This document has been carefully reviewed for technical accuracy. In the event that technical or typographical errors exist, TEDIA® reserves the right to make changes to subsequent editions of this document without prior notice to holders of this edition.

TEDIA® provides this document "as is", without warranty of any kind, either expressed or implied, including, but not limited to, its particular purpose. TEDIA® reserves the right to make improvements and/or changes to this document, or to the products and/or the programs described in this document, at any time.

Information provided in this document is intended to be accurate and reliable. The reader should contact TEDIA®, if errors are suspected. In no event shall TEDIA® be held liable for any form of damage arising out of or related to this document or the information contained in it.

All brand names and trademarks used in this document are the property of their respective owners.

Manufacturing, sales office, service center, technical support and headquarters:

address: TEDIA spol. s r. o., Zabelska 12, 31211 Plzen, Czech Republic

website: https://www.tedia.eu

phone/e-mail: https://www.tedia.eu/contacts tech. support: https://www.tedia.eu/support

Copyright © 1994 - 2015 TEDIA® spol. s r. o.

# **Table of Contents**

7.8

7.9

Register IRCCNT0StrReg [RD]

Register IRCCNT0CWReg [WR]

| 1.         | General information                                                                                                                             |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.1        | Introduction                                                                                                                                    |

| 1.2        | Standard height and low-profile card design                                                                                                     |

| 1.3        | Firmware version                                                                                                                                |

| 1.4        | Where to get more information, technical support                                                                                                |

| <b>2.</b>  | PCI Express controller                                                                                                                          |

| 2.1        | Introduction                                                                                                                                    |

| 2.2        | PCI configuration register space                                                                                                                |

| 2.3        | Register's mapping                                                                                                                              |

| <b>3.</b>  | Functional registers                                                                                                                            |

| 3.1        | Registers overview                                                                                                                              |

| 3.2        | Splitting the address space into blocks                                                                                                         |

| 3.3        | Block of registers with 8-bit data (+0000 ÷ 03FC)                                                                                               |

| 3.4<br>3.5 | Block of DIO ports and edge detection circuits registers (+0400 ÷ 07FC)<br>Block of IRC counters and min/max detectors registers (+1000 ÷ 10FC) |

| 3.6        | Block of SSI interfaces registers (+1100 ÷ 11FC)                                                                                                |

| 3.7        | Block of diagnostic registers (+3F00 ÷ 3FFC)                                                                                                    |

| 4.         | Registers intended for digital inputs/outputs ports                                                                                             |

| 4.1        | Introduction                                                                                                                                    |

| 4.1        | Digital port functionality                                                                                                                      |

| 4.3        | Registers DINReg0,, DINReg2 [RD]                                                                                                                |

| 4.4        | Registers Register DINReg(2-0) [RD]                                                                                                             |

| 4.5        | Registers DOUTReg0, , DOUTReg2 [WR]                                                                                                             |

| 4.6        | Register DOUTReg(2-0) [WR]                                                                                                                      |

| 4.7        | Register DIOCfgReg [WR/RD]                                                                                                                      |

| <b>5.</b>  | Registers intended for DIO signal edge detection circuits                                                                                       |

| 5.1        | Introduction                                                                                                                                    |

| 5.2        | Registers DINREReg(x-x) and DINFEReg(x-x) [WR]                                                                                                  |

| 5.3        | Registers DINREStatusReg(x-x) and DINFEStatusReg(x-x) [RD]                                                                                      |

| 5.4        | Registers DINRECIReg(x-x) and DINFECIReg(x-x) [WR]                                                                                              |

| 5.5<br>5.6 | Registers DINREIRQReg(x-x) and DINFEIRQReg(x-x) [WR] Simplified schematic diagram of edge detection circuits register structure                 |

|            |                                                                                                                                                 |

| <b>6.</b>  | Registers intended for interrupt handling circuits                                                                                              |

| 6.1<br>6.2 | Introduction                                                                                                                                    |

| 6.3        | Interrupt handling circuit functionality Register INTEnReg [WR]                                                                                 |

| 6.4        | Register IRQCfgReg [WR]                                                                                                                         |

| 6.5        | Register IRQStatusReg [RD]                                                                                                                      |

| 6.6        | Register IRQClrReg [WR]                                                                                                                         |

| 6.7        | Register TimerReg [WR/RD]                                                                                                                       |

| 6.8        | Simplified schematics diagram of interrupt handling circuits register structure                                                                 |

| <b>7.</b>  | Registers intended for IRC counters circuits                                                                                                    |

| 7.1        | Introduction                                                                                                                                    |

| 7.2        | IRC counter circuit functionality                                                                                                               |

| 7.3        | Differences in PCT-83xx card registers                                                                                                          |

| 7.4        | Register IRCCNTCtrlReg [WR]                                                                                                                     |

| 7.5        | Register IRCCNTEnReg [WR]                                                                                                                       |

| 7.6<br>7.7 | Register IRCCNT0SetReg [WR] Register IRCCNT0RngReg [WR]                                                                                         |

| 1.1        | vesiere ivecutoriistes [MV]                                                                                                                     |

11.3

Address space BAR2

| 7.10       | Register IRCCNT0StatReg [RD]                                                 |

|------------|------------------------------------------------------------------------------|

| 7.11       | Register structure diagram                                                   |

| <b>8.</b>  | Registers for detecting min/max values of IRC counters                       |

| 8.1        | Introduction                                                                 |

| 8.2        | Minimum/maximum detector functionality                                       |

| 8.3        | Differences in PCT-83xx card registers                                       |

| 8.4        | Register IRCCNTMinMaxEnReg [WR]                                              |

| 8.5        | Register IRCCNTMinMaxCtrlReg [WR]                                            |

| 8.6        | Register IRCCNT0MinReg [RD]                                                  |

| 8.7        | Register IRCCNT0MaxReg [RD]                                                  |

| 9.         | Registers intended for SSI interfaces                                        |

| 9.1        | Introduction                                                                 |

| 9.2        | SSI interfaces circuit functionality                                         |

| 9.3        | Differences in PCT-83xx card registers                                       |

| 9.4        | Register SSICtrlReg [WR]                                                     |

| 9.5        | Register SSICfgReg [WR]                                                      |

| 9.6        | Register SSI0CfgReg [WR]                                                     |

| 9.7        | Register SSI0StrReg [RD]                                                     |

| 9.8        | Description of the SSI interface controller operation and register structure |

| <b>10.</b> | Diagnostic registers (common to all card types)                              |

| 10.1       | Introduction                                                                 |

| 10.2       | Register CardResetReg [WR]                                                   |

| 10.3       | Register CardResetStatusReg [RD]                                             |

| 10.4       | Register CardSerNrReg [RD]                                                   |

| 10.5       | Register CardIDReg [RD]                                                      |

| 10.6       | Register FPGATypeReg [RD]                                                    |

| 10.7       | Register FPGAVerReg [RD]                                                     |

| 11.        | Registers in address spaces BAR1 a BAR2                                      |

| 11.1       | Introduction                                                                 |

| 11.2       | Address space BAR1                                                           |

## 1. General information

#### 1.1 Introduction

This Programmer's Guide follows the PCT-8303/8306/8360/8363 card User's Guide (hereinafter all types referred as PCT-83xx) containing ...

- · basic technical data,

- · description of installation procedure

- and description of the connector pin assignment.

User's Guide is intended for a regular card user who only needs to install card and use it with already created programs. Unlike the User's Guide, the Programmer's Guide contains ...

- description of the PCI Express controller built into the card,

- · description of all functional registers of the card

- · and description of register-level programming.

Programmer's Guide therefore enables programming using a system driver with an API offering direct access to the registers (in the case of Windows it is the tedia\_ep4gxa.dll library), i.e. creating special programs or custom drivers (e.g. for various SCADA systems or for the Linux operating system).

## 1.2 Standard height and low-profile card design

DAQ PCI Express TEDIA cards are available in a standard height version (type designation PCT-83xx) and low-profile version (type designation PCT-83xx/LP). With the exception of the different locations of connectors and the applicable accessories, both version are identical and the information contained in this manual is therefore valid for both variants.

#### 1.3 Firmware version

Current firmware version at the time this document was issued:

FPGA - firmware type: 2D (represented by a value  $2D_H$ ) FPGA - firmware version: 0.2 (represented by a value  $02_H$ )

The FPGA firmware type is a control number assigned to the standard PCT-83xx firmware. A different number represents either an incorrect firmware configuration (for example, intended for a different card) or custom firmware.

The FPGA firmware version is an additional parameter that defines the card properties.

Note:

The features described in this document reflect the specified firmware version.

Later firmware versions (unless otherwise noted) will be backward compatible with the current version and will include improvements to existing functionality or brand new features.

## 1.4 Where to get more information, technical support

Further useful information is available at...

website: https://www.tedia.eu

In doubt, you can contact the manufacturer's technical support:

address: TEDIA spol. s r. o., Zabelska 12, 31211 Plzen, Czech Republic

phone/e-mail: https://www.tedia.eu/contacts tech. support: https://www.tedia.eu/support

**Note:** Although this Programmer's Guide has been carefully reviewed, it can contain errors. If you suspect that some information is listed incorrectly, incompletely or inaccurately, please contact technical support.

## 2. PCI Express controller

#### 2.1 Introduction

All PCT-83xx cards are equipped with a PCI Express bus controller core implemented in an FPGA gate array (i.e. the cards do not use any special PCI Express controller/bridge to the local bus interconnecting I/O peripherals).

The implementation of controller is single-functional (the card thus behaves as one PCI device) with three address spaces (BAR) mapped in the in 32-bit address MEM space.

Note:

Although the card's registers are mapped to the MEM space with 32-bit addressing, the DMA controller (if implemented) supports both 32-bit and 64-bit addressing modes.

### 2.2 PCI configuration register space

The table below provides an overview of the selected registers from the PCI configuration register space.

| address                          | register name       | PCT-8303                                                                                               | PCT-8306             | PCT-8363             | PCT-8360          |

|----------------------------------|---------------------|--------------------------------------------------------------------------------------------------------|----------------------|----------------------|-------------------|

|                                  |                     | PCT-8303/LP                                                                                            | PCT-8306/LP          | PCT-8363/LP          | PCT-8360/LP       |

| 01 <sub>H</sub> ÷00 <sub>H</sub> | Vendor ID           | 1760 <sub>H</sub> (i.e. VID TEDI                                                                       | A)                   |                      |                   |

| 03 <sub>H</sub> ÷02 <sub>H</sub> | Device ID           | 0810 <sub>H</sub>                                                                                      | 0811 <sub>H</sub>    | 0812 <sub>H</sub>    | 0820 <sub>H</sub> |

| 08 <sub>H</sub>                  | Revision ID         | 118000 <sub>H</sub> (i.e. PCI cla                                                                      | ıss "other data acqu | isition controller") |                   |

| 0B <sub>H</sub> ÷09 <sub>H</sub> | Class Code          | functional card's re<br>(MEM, 16kB, assign                                                             | ~                    |                      |                   |

| 13 <sub>H</sub> ÷10 <sub>H</sub> | BAR0                | service purpose registers (firmware update, calibration constants, etc.) (MEM, 16kB, assigned by BIOS) |                      |                      |                   |

| 17 <sub>H</sub> ÷14 <sub>H</sub> | BAR1                | registers intended for the kernel part of the operating system driver (MEM, 4kB, assigned by BIOS)     |                      |                      |                   |

| 1B <sub>H</sub> ÷18 <sub>H</sub> | BAR2                | unused                                                                                                 |                      |                      |                   |

| 1F <sub>H</sub> ÷1C <sub>H</sub> | BAR3                | unused                                                                                                 |                      |                      |                   |

| 23 <sub>H</sub> ÷20 <sub>H</sub> | BAR4                | unused                                                                                                 |                      |                      |                   |

| 27 <sub>H</sub> ÷24 <sub>H</sub> | BAR5                | 1760 <sub>H</sub> (i.e. TEDIA VID)                                                                     |                      |                      |                   |

| $2D_{H} \div 2C_{H}$             | Subsystem Vendor ID | 0001 <sub>H</sub>                                                                                      |                      |                      |                   |

| $2F_{H} \div 2E_{H}$             | Subsystem ID        | number of IRQ channel (assigned by BIOS)                                                               |                      |                      |                   |

| 3C <sub>H</sub>                  | Interrupt Line      | O1 <sub>H</sub> (INTA)                                                                                 |                      |                      |                   |

| 3D <sub>H</sub>                  | Interrupt Pin       | O1 <sub>H</sub> (INTA)                                                                                 |                      |                      |                   |

#### What is the information provided by the PCI configuration registers described above ...

- Vendor ID and Device ID are intended for identification of the card type in the system (in case of uncertainty, Subsystem Vendor ID and Subsystem ID may also be used, or Class Code)

- BARx are designed to determine the allocated resources, i.e. the starting address of the register blocks

- The Interrupt Line is designed to determine the current connection of the card's INT signal to the logic IRQ interrupt channel (resp. to the MSI channel in case of this interrupt mode)

## 2.3 Register's mapping

The following paragraphs describe general information about register mapping.

#### Register's mapping only in MEM space and not in I/O space as with TEDIA DAQ PCI cards ...

Mapping in I/O space is obsolete and very restrictive (it allows to allocate a total of 255 blocks of 256 bytes size to all PCI devices in the computer) and finds meaningful use only in operating systems (resp. development tools) that do not allow simple 32-bit or 64-bit addressing of MEM space (eg. MS-DOS).

#### Registers in BAR0 space ...

This BAR space contains all user registers (i.e. registers accessing I/O peripherals of the card).

The following chapters are dedicated, with a few exceptions, exclusively on the description of these registers.

#### Registers in BAR1/BAR2 space ...

These BAR spaces contain service purpose registers and registers intended for kernel part of the operating system driver.

#### **Functional registers** 3.

#### 3.1 **Registers overview**

The tables in the following paragraphs provide an overview of the functional registers implemented in the current firmware version (see Chapter 1). All functional registers described in this chapter are mapped in BAR0 space.

Warning: All registers, unless explicitly stated otherwise (e.g. registers whose initial value can be defined via the EEPROM contents), have zero values after power-up start or reset.

However, when program starts, it can not rely on this state because the registers can be set to different values by the previous program; they can be set to defined state either by programming values or by using the CardResetReg register.

Note:

If you are creating a program that supports multiple types of card, it is also recommended to use a document containing tables with comparison of register maps for different types of cards.

#### **3.2** Splitting the address space into blocks

The table below provides an overview of splitting of the entire BAR0 address space into several blocks according to I/O peripherals; this structure is used by all types of TEDIA DAQ PCI Express card.

| offset within BAR0                                                                        | description of registers block                                                 |

|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| +0000 ÷ 03FC registers with 8-bit data (intended for easier migration from DAQ PCI cards) |                                                                                |

| +0400 ÷ 07FC                                                                              | registers with 32-bit data (block of DIO ports and edge detection circuits)    |

| +0800 ÷ 0FFC                                                                              | registers with 32-bit data (PCT-83xx does not use this block)                  |

| +1000 ÷ 10FC                                                                              | registers with 32-bit data (block of IRC counters including min/max detectors) |

| +1100 ÷ 11FC                                                                              | registers with 32-bit data (block of SSI interfaces)                           |

| +1000 ÷ 3EFC                                                                              | registers with 32-bit data (PCT-83xx does not use this block)                  |

| +3F00 ÷ 3FFC                                                                              | diagnostic registers (common to all types of cards)                            |

#### 3.3 Block of registers with 8-bit data (+0000 ÷ 03FC)

The table below provides a list of registers with 8-bit data.

The registers can be accessed with byte operand to the address specified in the table, or with dword operand, with valid data being transmitted on the lowest eight bits (higher bits are ignored during writing and zeroed during reading).

The program can only access addresses aligned to the dword (i.e. in integer multiple of 4) and it is not recommended to access addresses other than listed in the table.

| offset within BARO | description of register (write) | description of register (read) |

|--------------------|---------------------------------|--------------------------------|

| +0000              | DOUTReg0                        | DINReg0                        |

| +0004              | DOUTReg1                        | DINReg1                        |

| +0008              | DOUTReg2                        | DINReg2                        |

| +0080              | DIOCfgReg                       | (read back the register value) |

| +0200              | IRQCfgReg                       | IRQStatusReg                   |

| +0204              | IRQCIrReg                       |                                |

| +0208              | TimerReg                        | TimerReg                       |

| +020C              | INTEnReg                        | (read back the register value) |

| +03F4              |                                 | CardIDReg                      |

| +03F8              |                                 | FPGATypeReg                    |

| +03FC              |                                 | FPGAVerReg                     |

Note: The register mapping of the first three DIO ports is identical for all TEDIA DAQ PCIe cards.

#### 3.4 Block of DIO ports and edge detection circuits registers (+0400 ÷ 07FC)

The table below provides a list of registers dedicated for access to DIO ports and signal rising/falling edge detection circuits with the possibility of triggering an interrupt.

The program can only access registers with dword operand at addresses aligned to the dword (i.e. in integer multiple of 4) and it is not recommended to access addresses other than listed in the table.

| offset within BAR0 | description of register (write) | description of register (read) |

|--------------------|---------------------------------|--------------------------------|

| +0400              | DOUTReg(2-0)                    | DINReg(2-0)                    |

| +0410              | DINREReg(2-0)                   | DINREStatusReg(2-0)            |

| +0414              | DINRECIrReg(2-0)                |                                |

| +0418              | DINFEReg(2-0)                   | DINFEStatusReg(2-0)            |

| +041C              | DINFECIrReg(2-0)                |                                |

| +0440              | DINREIRQReg(2-0)                | (read back the register value) |

| +0444              | DINFEIRQReg(2-0)                | (read back the register value) |

#### 3.5 Block of IRC counters and min/max detectors registers (+1000 ÷ 10FC)

The table below provides a list of registers dedicated for access to registers of IRC counters and min/max detectors.

The program can only access registers with dword operand at addresses aligned to the dword (i.e. in integer multiple of 4) and it is not recommended to access addresses other than listed in the table.

The register block on addresses +1000 ÷ 101C contains the registers of the first IRC counter and related config/status functions (i.e. IRCCNT0SetReg, IRCCNT0CWReg, IRCCNT0RngReg, IRCCNT0CWReg, IRCCNT0StatReg, IRCCNT0MinReg and IRCCNT0MaxReg). The analogous structure of the registers for IRC counters IRCCNT1 - IRCCNT5 is mapped to following addresses and these register blocks have exactly the same functionality as the registers block of IRCCNT0.

| offset within BAR0 | description of register (write)                                   | description of register (read) |  |

|--------------------|-------------------------------------------------------------------|--------------------------------|--|

| +1000              | IRCCNT0SetReg                                                     | IRCCNT0StrReg                  |  |

| +1004              | IRCCNT0RngReg                                                     |                                |  |

| +1008              |                                                                   |                                |  |

| +100C              |                                                                   |                                |  |

| +1010              | IRCCNT0CWReg                                                      | IRCCNT0StatReg                 |  |

| +1014              |                                                                   |                                |  |

| +1018              |                                                                   | IRCCNT0MinReg                  |  |

| +101C              |                                                                   | IRCCNT0MaxReg                  |  |

| +1020 ÷ +103C      | registers of IRCCNT1 (structure analogous to block +1000 ÷ +101C) |                                |  |

| +1040 ÷ +105C      | registers of IRCCNT2 (structure analogous to block +1000 ÷ +101C) |                                |  |

| +1060 ÷ +107C      | registers of IRCCNT3 (structure analogous to block +1000 ÷ +101C) |                                |  |

| +1080 ÷ +109C      | registers of IRCCNT4 (structure analogous to block +1000 ÷ +101C) |                                |  |

| +10A0 ÷ +10BC      | registers of IRCCNT5 (structure analogous to block +1000 ÷ +101C) |                                |  |

| +10C0              | IRCCNTEnReg                                                       | (read back the register value) |  |

| +10C4              | IRCCNTCtrlReg                                                     |                                |  |

| +10C8              | IRCCNTMinMaxEnReg                                                 | (read back the register value) |  |

| +10CC              | IRCCNTMinMaxCtrlReg                                               |                                |  |

The table above shows the registers for a set of six IRC counters, however, their implementation depends on the number of IRC counters of the card type.

| interface                | PCT-8303 (/LP) | PCT-8306 (/LP) | PCT-8363 (/LP) | PCT-8360 (/LP) |

|--------------------------|----------------|----------------|----------------|----------------|

| number of IRC counters   | 3 (CNT0÷CNT2)  | 6 (CNT0÷CNT5)  | 3 (CNT0÷CNT2)  | 0              |

| number of SSI interfaces | 0              | 0              | 6 (SSI0÷SSI5)  | 6 (SSI0÷SSI5)  |

#### 3.6 Block of SSI interfaces registers (+1100 ÷ 11FC)

The table below provides a list of registers dedicated for access to registers of SSI interfaces.

The program can only access registers with dword operand at addresses aligned to the dword (i.e. in integer multiple of 4) and it is not recommended to access addresses other than listed in the table.

The register block on addresses +1100 ÷ 111C contains the registers of the first SSI interface and related config/status functions (i.e. SSI0CfgReg and SSI0StrReg). The analogous structure of the registers for SSI interfaces SSI1 - SSI5 is mapped to following addresses and these register blocks have exactly the same functionality as the registers block of SSI0.

| offset within BAR0 | description of register (write)                                 | description of register (read) |  |

|--------------------|-----------------------------------------------------------------|--------------------------------|--|

| +1100              |                                                                 | SSI0StrReg                     |  |

| +1104              |                                                                 |                                |  |

| +1108              |                                                                 |                                |  |

| +110C              |                                                                 |                                |  |

| +1110              | SSI0CfgReg                                                      | (zpětné čtení)                 |  |

| +1114              |                                                                 |                                |  |

| +1118              |                                                                 |                                |  |

| +111C              |                                                                 |                                |  |

| +1120 ÷ +113C      | registers of SSI1 (structure analogous to block +11100 ÷ +111C) |                                |  |

| +1140 ÷ +115C      | registers of SSI2 (structure analogous to block +11100 ÷ +111C) |                                |  |

| +1160 ÷ +117C      | registers of SSI3 (structure analogous to block +11100 ÷ +111C) |                                |  |

| +1180 ÷ +119C      | registers of SSI4 (structure analogous to block +11100 ÷ +111C) |                                |  |

| +11A0 ÷ +11BC      | registers of SSI5 (structure analogous to block +11100 ÷ +111C) |                                |  |

| +11C0              | SSICfgReg                                                       | (read back the register value) |  |

| +11C4              | SSICtrlReg                                                      |                                |  |

The table above shows the registers for a set of six SSI interfaces, however, their implementation depends on the number of SSI interfaces of the card type.

| interface                | PCT-8303 (/LP) | PCT-8306 (/LP) | PCT-8363 (/LP) | PCT-8360 (/LP) |

|--------------------------|----------------|----------------|----------------|----------------|

| number of IRC counters   | 3 (CNT0÷CNT2)  | 6 (CNT0÷CNT5)  | 3 (CNT0÷CNT2)  | 0              |

| number of SSI interfaces | 0              | 0              | 6 (SSI0÷SSI5)  | 6 (SSI0÷SSI5)  |

## 3.7 Block of diagnostic registers (+3F00 ÷ 3FFC)

The table below provides a list of registers dedicated for access to diagnostic and identification functions.

The program can only access registers with dword operand at addresses aligned to the dword (i.e. in integer multiple of 4) and it is not recommended to access addresses other than listed in the table.

| offset within BAR0 | description of register (write) | description of register (read) |

|--------------------|---------------------------------|--------------------------------|

| +3FE0              | CardResetReg                    | CardResetStatusReg             |

| +3FF0              |                                 | CardIDReg                      |

| +3FF4              |                                 | CardSerNrReg                   |

| +3FF8              |                                 | FPGATypeReg                    |

| +3FFC              |                                 | FPGAVerReg                     |

## 4. Registers intended for digital inputs/outputs ports

#### 4.1 Introduction

The following sections describe the registers related to digital inputs and outputs (see the overview in Chapter 3). The DIO registers can be divided into a group of data registers...

DINReg0, ...2 three 8-bit digital port input registers (sets of signals DIO00÷07, DIO08÷15 and DIO16÷23)

DINReg(2-0) 32-bit digital port input register (combines DINReg0, DINReg1 and DINReg2)

DOUTReg0, ...2 three 8-bit digital port output registers (sets of signals DIO00÷07, DIO08÷15 and DIO16÷23)

DOUTReg(2-0) 32-bit digital port output register (combines DOUTReg0, DOUTReg1 and DOUTReg2)

and configuration register...

DIOCfgReg register for configuration of direction DIO ports (i.e. selection of input or output port)

Note:

Initial value (e.g. after power-up or soft-reset using the CardResetReg register) of all registers mentioned above can be defined via the EEPROM contents. Because the initial values stored in the EEPROM can be modified by the configuration program, the user can define the DIO ports status programmed immediately after turning on the computer without delay until the program starts.

#### 4.2 Digital port functionality

All three ports are designed as bidirectional, i.e. each port (= eight digital signals) can be individually set as input or output. The current state of the port can be obtained by reading the DINx register; in the case of configuration as an input port, the status of input signals is read, in the case of configuration as an output port, current data written to the output register are read back.

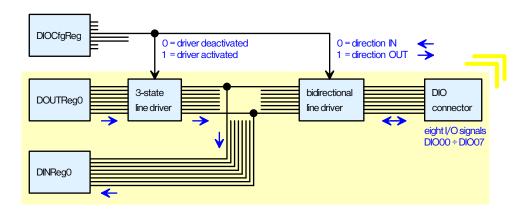

Further details can be seen in the picture below (only 8-bit port DIO0 is drawn, the part with the yellow background is included in the card three times, i.e. separately for DIO0, DIO1 and DIO2 port).

#### Location of ports on the card connectors

All three ports (i.e. DIO0, DIO1 and DIO2) are connected to the KX1 - KX3 connectors located on the back edge of the card (they are accessible via adapter cable), the next three ports (i.e. DIO0, DIO1 and DIO2) are connected to the D-Sub 25 connector located on the card bracket.

**Note:** The register mapping of the three DIO ports described above is identical for all TEDIA DAQ PCIe cards.

DO

## 4.3 Registers DINReg0, ..., DINReg2 [RD]

These registers are used to read the status of the digital port, each bit of the register accesses one signal of the 8-bit digital port (bits D0 of these registers access the signals DIO00/08/16; bits D7 access DIO07/15/23).

In the case the port is configured as an input port, the register provides a current status of input signals; in the case the port is configured as an output port, current data written to the output register are read back.

## 4.4 Register DINReg(2-0) [RD]

This register is an an alternative to the 8-bit registers described in the previous paragraph and they are used to read the status of three digital ports at once (functionality remains identical to 8-bit registers).

The DINReg(2-0) register combines DINReg0, DINReg1 and DINReg2 (bits D00÷D23 provide a current value of ports DIO00÷DIO23, the highest eight bits are permanently zeroed).

## 4.5 Registers DOUTReg0, ..., DOUTReg2 [WR]

These registers are used to control the status of the output digital port, each bit of the register defines one signal of the 8-bit digital port (bits D0 of the registers control the signals DIO00/08/16; bits D7 control DIO07/15/23).

In the case the port is configured as an input port, data can be written to the DOUTReg register, but its contents do not affect the state of the signals. In the case the port is configured as an output port, the current contents of this register defines the status of the output signals.

Writing to these registers is allowed even if the port is set as input, their contents will be transferred to the signals immediately after the port is switched to output mode.

## 4.6 Register DOUTReg(2-0) [WR]

This register is an alternative to the 8-bit registers described in the previous paragraph and it is used to control the contents of three digital ports at once (functionality remains identical to 8-bit registers).

The DOUTReg(2-0) register combines DOUTReg0, DOUTReg1 and DOUTReg2 (bits D00÷D23 define the status of the output signal DIO00÷DIO23, the highest eight bits are ignored).

**D4**

## 4.7 Register DIOCfgReg [WR/RD]

D6

D7

**RSRV**

This register is used to configure bidirectional DIO ports as input or output.

**D5**

| RSRV |                                    | DIR2                                                                         | DIR1 | DIR0 |

|------|------------------------------------|------------------------------------------------------------------------------|------|------|

| DIR0 |                                    | ter are deactivated (i.e. the port v                                         | •    | *    |

| DIR1 | direction control of the DIO1 port | ter are activated (i.e. the port won<br>ter are deactivated (i.e. the port v | • •  |      |

| DIR2 | •                                  | ter are activated (i.e. the port wo                                          | •    |      |

|      | •                                  | ter are deactivated (i.e. the port veter are activated (i.e. the port wo     | •    |      |

**D3**

reserved (to ensure forward compatibility it is recommended to write 0 and ignore readed value)

D2

D1

# 5. Registers intended for DIO signal edge detection circuits

#### 5.1 Introduction

The following sections describe the registers related to signal edge detection circuits (see the overview in Chapter 3). List of registers:

DINREReg(2-0) enable of rising edge detection on DIO00÷DIO23 port signals

DINREStatusReg(2-0) rising edge event flags on DIO00÷DIO23 port signals

DINREClrReg(2-0) clear rising edge event flags on DIO00÷DIO23 port signals

DINFEReg(2-0) enable of falling edge detection on DIO00÷DIO23 port signals

DINFEStatusReg(2-0) falling edge event flags on DIO00÷DIO23 port signals

DINFECIrReg(2-0) clear falling edge event flags on DIO00÷DIO23 port signals

DINREIRQReg(2-0) enable interrupts from edge detection circuits (rising edge detection on DIO00÷DIO23)

DINFEIRQReg(2-0) enable interrupts from edge detection circuits (falling edge detection on DIO00÷DIO23)

## 5.2 Registers DINREReg(x-x) and DINFEReg(x-x) [WR]

These registers are intended to enable rising edge detection (DINREReg), resp. falling edge detection (DINFEReg) on DIO port signals.

These registers have significant 24 lowest bits (bit D0 with value 1 enable edge detection on signal DIO00; bit D23 with value 1 enable edge detection on signal DIO23), the highest eight bits are ignored (value 0 recommended to ensure forward compatibility).

## 5.3 Registers DINREStatusReg(x-x) and DINFEStatusReg(x-x) [RD]

These registers are intended to determine the status of the flags of the edge detection circuits enabled by the DINREReg(x-x) and DINFEReg(x-x) registers.

These registers have significant 24 lowest bits (value 1 on bit D0 indicate active flags related to signal DIO00; value 1 on bit D23 indicate active flags related to signals DIO23), the highest eight bits are permanently zeroed.

#### 5.4 Registers DINREClrReg(x-x) and DINFEClrReg(x-x) [WR]

These registers are intended to clearing selected flags of the edge detection circuits.

These registers have significant 24 lowest bits (bit D0 with value 1 clear flags related to signal DIO00, bit D23 with value 1 clear flags related to signal DIO23), the highest eight bits are ignored (value 0 recommended to ensure forward compatibility).

Writing a value of 1 to a defined bit generates a short pulse, so following write of 0 is not required. Clearing any combination of flags in a single write cycle is allowed.

## 5.5 Registers DINREIRQReg(x-x) and DINFEIRQReg(x-x) [WR]

These registers are intended to enable system interrupt event generation related to edge detection circuit flags.

These registers have significant 24 lowest bits (bit D0 with value 1 enable interrupt event generation related to signal DIO00; bit D23 with value 1 enable interrupt event generation related to signal DIO23), the highest eight bits are ignored (value 0 recommended to ensure forward compatibility).

More detailed information can be found in the picture and description given in the following paragraph, resp. in a separate chapter with a description of interrupt circuits.

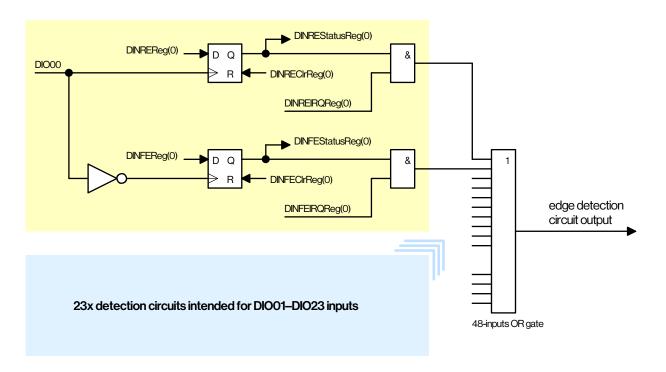

## 5.6 Simplified schematic diagram of edge detection circuits register structure

The figure below shows a simplified schematic diagram of the edge detection circuits, the connection with interrupt circuits is described in a separate chapter.

Each DIOxx signal is equipped with identical circuits that allow the independent detection of rising edge, falling edge or both edges on this signal.

The part of the schematics diagram highlighted in yellow shows the circuits dedicated for processing the signal DIO00, the blue marked part shows the identical circuits for the signals DIO01 to DIO23.

All 48 flags (available for reading via the DINREStatus and DINFEStatus registers) allow to trigger an interrupt. Flags are processed by AND gates in the first step (DINREIRQReg and DINFEIRQReg with value 1 allow flags signal to pass through AND gate) and in the second step by OR gate.

As can be seen from the schematics diagram of the interrupt circuits (see the description in a separate chapter), the interrupt of the system is triggered by the first detected edge, i.e. by transitioning the OR gate output from 0 to 1. To further trigger an interrupt, it is therefore necessary for the interrupt program handler to process all interrupt events and then clear all the flags of the edge detection circuits.

# 6. Registers intended for interrupt handling circuits

#### 6.1 Introduction

The following sections describe the registers related to interrupt handling circuits (see the overview in Chapter 3).

List of registers:

INTEnReg interconnection of interrupt detection circuits (all registers described in this chapter) with card

interrupt generation circuits (both INTA or MSI mode)

IRQCfgReg enabling of general interrupt sources

IRQStatusReg statuses of general interrupt sources

IRQClrReg clearing of general interrupt flags

TimerReg timestamp generator for periodically triggering interrupts

## 6.2 Interrupt handling circuit functionality

Interrupt handling circuits have the capability to cause a system interrupt event by one of the sources, or by a selected combination of interrupt sources. The card uses the following interrupt sources:

#### Timestamp generator

Allows to trigger an interrupt with a selected time period in the range of 1÷254 ms.

#### Digital inputs - simple mode compatible with DAQ PCI cards

Allows to trigger an interrupt with falling edge of selected DIO port signals.

#### Digital inputs - edge detection circuits used by DAQ PCI Express cards

Allows to trigger an interrupt by any combination of rising and falling edges on all DIO port signals.

Note:

For proper function of the interrupt circuits (see the schematics diagram on the following pages) it is necessary to consider, that interrupt of the system is triggered by the first event. To further trigger an interrupt, it is therefore necessary for the interrupt program handler to process all interrupt events and then clear all the flags (optional flags of the edge detection circuits).

#### 6.3 Register INTEnReg [WR]

These registers are intended to interconnection of interrupt detection circuits (all registers described in this chapter) with card interrupt generation circuits (both INTA or MSI mode).

| D7    | D6   | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|------|----|----|----|----|----|----|

| INTEN | RSRV |    |    |    |    |    |    |

INTEN activation of INTA/MSI control circuits

capture register generating control signal INTA or generating MSI is permanently zeroed the capture register function is activated, i.e. the card may triggered a system interrupt

RSRV reserved (to ensure forward compatibility it is recommended to write 0)

## 6.4 Register IRQCfgReg [WR]

These registers are intended to enable of general interrupt sources.

| D7   | D6                                                                                                                                                  | D5              | D4              | D3         | D2   | D1   | DO   |  |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------|------------|------|------|------|--|

| RSRV | DIN-X                                                                                                                                               | RSRV            | TIM             | RSRV       | IRQ2 | IRQ1 | IRQ0 |  |

| IRQ0 | enables the trigger an interrupt derived from the falling edge of digital port DIO00  the capture register connected with digital input is disabled |                 |                 |            |      |      |      |  |

|      | 1 the ca                                                                                                                                            | apture register | functionality i | is enabled |      |      |      |  |

IRQ1 enables the trigger an interrupt derived from the falling edge of digital port DIO08 the capture register connected with digital input is disabled the capture register functionality is enabled 1 IRQ2 enables the trigger an interrupt derived from the falling edge of digital port DIO16 the capture register connected with digital input is disabled the capture register functionality is enabled TIM enables the trigger an interrupt derived from timestamp generator the capture register connected with timestamp generator is disabled the capture register functionality is enabled 1 DIN-X enables the trigger an interrupt derived from signal edge detection circuits the capture register connected with signal edge detection circuits

the capture register functionality is enabled

## 6.5 Register IRQStatusReg [RD]

1

RSRV

This register is intended to determine the status of the capture registers enabled by the IRQCfgReg register.

reserved (to ensure forward compatibility it is recommended to write 0)

| D7   | D6    | D5   | D4  | D3   | D2   | D1   | D0   |

|------|-------|------|-----|------|------|------|------|

| RSRV | DIN-X | RSRV | TIM | RSRV | IRQ2 | IRQ1 | IRQ0 |

| IRQ0  | the current status of the capture register connected with digital input DIO00                        |

|-------|------------------------------------------------------------------------------------------------------|

|       | 0 the register is not set, i.e. no falling edge has been detected since the last reset               |

|       | the register is set, i.e. an interrupt request event has occurred since the last reset               |

| IRQ1  | the current status of the capture register connected with digital input DIO08                        |

|       | 0 the register is not set, i.e. no falling edge has been detected since the last reset               |

|       | the register is set, i.e. an interrupt request event has occurred since the last reset               |

| IRQ2  | the current status of the capture register connected with digital input DIO16                        |

|       | 0 the register is not set, i.e. no falling edge has been detected since the last reset               |

|       | the register is set, i.e. an interrupt request event has occurred since the last reset               |

| TIM   | the current status of the capture register connected with timestamp generator                        |

|       | 0 the register is not set, i.e. no tome stamp has been detected since the last reset                 |

|       | the register is set, i.e. an interrupt request event has occurred since the last reset               |

| DIN-X | the current status of the capture register connected with edge detection circuits                    |

|       | the register is not set, i.e. no edge detection circuit event has been detected since the last reset |

|       | the register is set, i.e. an interrupt request event has occurred since the last reset               |

| RSRV  | reserved (to ensure forward compatibility it is recommended to ignore readed value)                  |

|       |                                                                                                      |

## 6.6 Register IRQClrReg [WR]

This register is intended to clearing selected flags enabled by the IRQCfgReg register.

| D7   | D6    | D5   | D4  | D3   | D2   | D1   | D0   |

|------|-------|------|-----|------|------|------|------|

| RSRV | DIN-X | RSRV | TIM | RSRV | IRQ2 | IRQ1 | IRQ0 |

| IRO0  | resets the capture register connected with digital input DIO00          |

|-------|-------------------------------------------------------------------------|

| INQU  |                                                                         |

|       | 0 idle write, the state of the capture register is not modified         |

|       | 1 the capture register is reset (subsequent writing 0 is not required)  |

| IRQ1  | resets the capture register connected with digital input DIO08          |

|       | 0 idle write, the state of the capture register is not modified         |

|       | 1 the capture register is reset (subsequent writing 0 is not required)  |

| IRQ2  | resets the capture register connected with digital input DIO16          |

|       | 0 idle write, the state of the capture register is not modified         |

|       | 1 the capture register is reset (subsequent writing 0 is not required)  |

| TIM   | resets the capture register connected with timestamp generator          |

|       | 0 idle write, the state of the capture register is not modified         |

|       | 1 the capture register is reset (subsequent writing 0 is not required)  |

| DIN-X | resets the capture register connected with edge detection circuits      |

|       | 0 idle write, the state of the capture register is not modified         |

|       | 1 the capture register is reset (subsequent writing 0 is not required)  |

| RSRV  | reserved (to ensure forward compatibility it is recommended to write 0) |

## 6.7 Register TimerReg [WR/RD]

This register is intended to control a timestamp generator intended mainly to periodically trigger a system interrupt.

The initial value of the register is zero and the timestamp generator is stopped. By writing a non-zero value, the generator is started, the period is defined by the written value in milliseconds (up to 254 ms). By writing a zero value, the generator is stopped again.

The register is also important for reading (this register provides a current value of the timestamp counter incremented from zero every millisecond to the entered value reduced by one).

For example, by writing a value of 100, the first interrupt is triggered 100 ms after writing to the register and then every 100 ms. The values 0, 1, ..., 98, 99, 0, 1, ..., are provided by reading this register, the system interrupt is triggered at the moment of transition from 99 to 0.

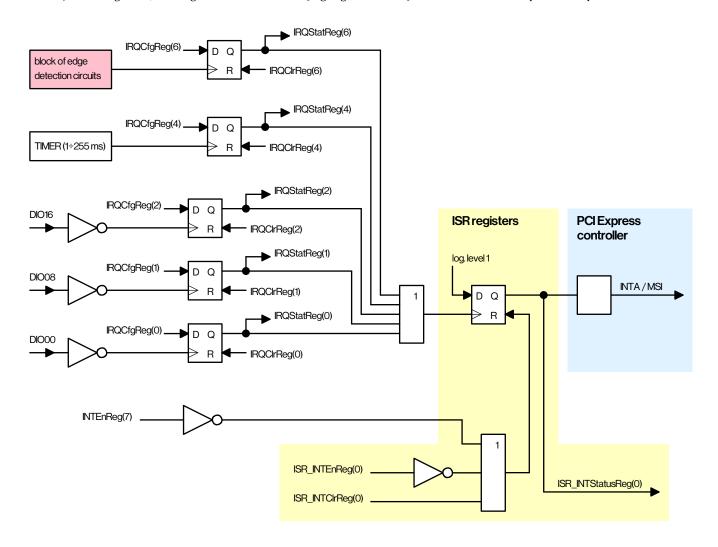

## 6.8 Simplified schematics diagram of interrupt handling circuits register structure

The figure below shows a simplified schematic diagram of the interrupt handling circuits and interconnection with control/status registers; the edge detection circuits (highlighted in red) are described in a separate chapter.

**Note:** All three ISR\_\*\*\* registers are mapped in BAR2 space and their description is out of focus of this manual.

From a general point of view - the circuits highlighted with yellow background must be controlled within the ISR (i.e. in the OS kernel), the others can be controlled within the user program, within application driver (e.g. in the case of Windows, the DLL with an API containing abstract high-level functions) or also within the ISR.

The ISR\_INTEnReg(0), ISR\_INTClrReg(0) and ISR\_INTStatusReg(0) signals are implemented identically on all TEDIA DAQ PCIe cards and allow to unify the ISR. The ISR\_INTEnReg(0) signal is set to 1 after a power-up start or reset, therefore control via INTEnReg(7) can be also used to create a user specific kernel driver without the need for knowledge of mapping ISR registers in BAR2 space.

Internal solution of the standard tedia\_ep4gxa driver for Windows fully complies with the information described above; the ISR\_INTEnReg(0) and ISR\_INTClrReg(0) signals are controlled from the kernel part of this driver, as the only status information is used ISR\_INTStatusReg(0). The ISR is therefore completely independent of the type of card.

**Note:** Detailed information on interrupt handling register control is provided in the document "DAQ PCI/PCIe card's Windows system driver Programmer's Guide".

## 7. Registers intended for IRC counters circuits

#### 7.1 Introduction

The following sections describe the registers related to IRC counters circuits (see the overview in Chapter 3).

Registers can be divided into a group common to all IRC counters

IRCCNTEnReg register intended for enabling counting or resetting by external signals

IRCCNTCtrlReg register intended for setting the counter value, or capturing the current value into the registers and a group of registers implemented separately for each counter (the registers have names IRCCNT0..., IRCCNT1..., etc.)

IRCCNTxSetReg registers intended for data written to the "x<sup>th</sup>" counter

IRCCNTxRngReg registers intended for configuring the counting range of the "xth" counter

IRCCNTxStrReg registers intended for capturing data from the "x<sup>th</sup>" counter

IRCCNTxCWReg registers intended for configuring the "x\*\*" counter

IRCCNTxStatReg registers intended for status information of the "x<sup>th</sup>" counter

Note:

The contents of all registers listed above except of IRCCNTxRngReg are set to zero after power-up or reset (including the reset triggered by the CardResetReg register). The value of all IRCCNTxRngReg registers is set to the maximum value, i.e. FFFFFFFF<sub>IP</sub>

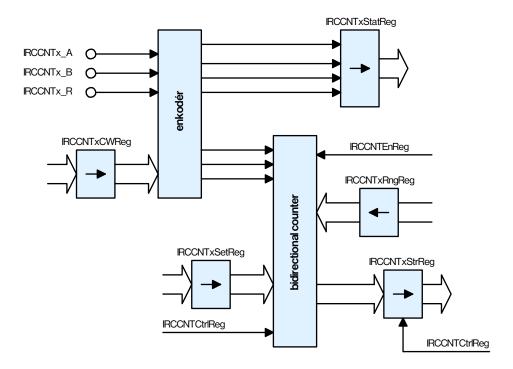

#### 7.2 IRC counter circuit functionality

The following paragraphs will describe typical counter program operations.

#### Counter configuration (described for counter IRCCNT0)

The IRCCNT0CWReg and IRCCNT0RngReg registers are used for configuration, allowing you to set the counter mode and counting range. Subsequently, the counter value can be set using IRCCNT0SetReg (or also IRCCNTCtrlReg).

It is recommended to check the status of the IRCCNT0StatReg register (error flag) and, if necessary, reset it using the IRCCNT0CWReg register.

#### Starting counters (described for counter IRCCNT0)

The IRCCNTEnReg register is used to start and stop counters (i.e. respond to input signals).

#### Software reading of counters (described for counter IRCCNT0)

Reading the counters takes place in two phases; in the first phase, the value of the counter (or selected counters) is captured into the buffer registers using IRCNCNTCtrllReg and in the second phase, the captured value is read using IRCCNT0StrReg.

Note:

Capturing the counter value with an external signal and stream reading using a FIFO is being prepared for future versions of the FPGA firmware.

#### 7.3 Differences in PCT-83xx card registers

The PCT-83xx cards differ only in the number of IRC counters or the number of SSI interfaces.

| interface                | PCT-8303 (/LP) | PCT-8306 (/LP) | PCT-8363 (/LP) | PCT-8360 (/LP) |

|--------------------------|----------------|----------------|----------------|----------------|

| number of IRC counters   | 3 (CNT0÷CNT2)  | 6 (CNT0÷CNT5)  | 3 (CNT0÷CNT2)  | 0              |

| number of SSI interfaces | 0              | 0              | 6 (SSI0÷SSI5)  | 6 (SSI0÷SSI5)  |

The following paragraphs will describe the full register structure for six IRC counters, with the understanding that for cards with three or no IRC counters, the registers, or the corresponding bits in the common registers, are not implemented.

## 7.4 Register IRCCNTCtrlReg [WR]

This register is intended to software capture of the current IRC counter value into the capture registers and also for setting the counter value according to preset values.

All bits can be used simultaneously in any combination, the counters allow simultaneous capturing and setting.

| D7   | D6   | D5       | D4       | D3       | D2       | D1       | D0       |

|------|------|----------|----------|----------|----------|----------|----------|

| RSRV | RSRV | STR_IRC5 | STR_IRC4 | STR_IRC3 | STR_IRC2 | STR_IRC1 | STR_IRC0 |

| D15  | D14  | D13      | D12      | D11      | D10      | D9       | D8       |

| RSRV | RSRV | RSRV     | RSRV     | RSRV     | RSRV     | RSRV     | RSRV     |

| D23  | D22  | D21      | D20      | D19      | D18      | D17      | D16      |

| RSRV | RSRV | SET_IRC5 | SET_IRC4 | SET_IRC3 | SET_IRC2 | SET_IRC1 | SET_IRC0 |

| D31  | D30  | D29      | D28      | D27      | D26      | D25      | D24      |

| RSRV | RSRV | RSRV     | RSRV     | RSRV     | RSRV     | RSRV     | RSRV     |

| STR_IRC0  | stores the current value of the IRCCNT0 counter in the IRCCNT0StrReg capture register                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

|           | 0 idle write, the state of the capture register is not modified                                                                             |

|           | data transferred to the capture register (subsequent writing 0 is not required)                                                             |

| STR_IRC1  | stores the current value of the IRCCNT1 counter in the IRCCNT1StrReg capture register                                                       |

|           | 0 idle write, the state of the capture register is not modified                                                                             |

|           | data transferred to the capture register (subsequent writing 0 is not required)                                                             |

| STR_IRC2  | stores the current value of the IRCCNT2 counter in the IRCCNT2StrReg capture register                                                       |

|           | 0 idle write, the state of the capture register is not modified                                                                             |

|           | data transferred to the capture register (subsequent writing 0 is not required)                                                             |

| STR_IRC3  | stores the current value of the IRCCNT3 counter in the IRCCNT3StrReg capture register                                                       |

|           | 0 idle write, the state of the capture register is not modified                                                                             |

|           | data transferred to the capture register (subsequent writing 0 is not required)                                                             |

| STR_IRC4  | stores the current value of the IRCCNT4 counter in the IRCCNT4StrReg capture register                                                       |

|           | 0 idle write, the state of the capture register is not modified                                                                             |

|           | data transferred to the capture register (subsequent writing 0 is not required)                                                             |

| STR_IRC5  | stores the current value of the IRCCNT5 counter in the IRCCNT5StrReg capture register                                                       |

|           | 0 idle write, the state of the capture register is not modified                                                                             |

|           | data transferred to the capture register (subsequent writing 0 is not required)                                                             |

| SET_IRC0  | stores the current value of the IRCCNT0SetReg preset register in the IRCCNT0 counter                                                        |

|           | 0 idle write, the state of the counter is not modified                                                                                      |

|           | data transferred to the counter (subsequent writing 0 is not required)                                                                      |

| SET_IRC1  | stores the current value of the IRCCNT1SetReg preset register in the IRCCNT1 counter                                                        |

|           | o idle write, the state of the counter is not modified                                                                                      |

|           | data transferred to the counter (subsequent writing 0 is not required)                                                                      |

| SET_IRC2  | stores the current value of the IRCCNT2SetReg preset register in the IRCCNT2 counter                                                        |

|           | 0 idle write, the state of the counter is not modified                                                                                      |

| 00m 10.00 | data transferred to the counter (subsequent writing 0 is not required)                                                                      |

| SET_IRC3  | stores the current value of the IRCCNT3SetReg preset register in the IRCCNT3 counter                                                        |

|           | 0 idle write, the state of the counter is not modified 1 data transferred to the counter (subsequent writing 0 is not required)             |

| CET IDC4  |                                                                                                                                             |

| SET_IRC4  | stores the current value of the IRCCNT4SetReg preset register in the IRCCNT4 counter 0 idle write, the state of the counter is not modified |

|           | data transferred to the counter (subsequent writing 0 is not required)                                                                      |

| SET_IRC5  | stores the current value of the IRCCNT5SetReg preset register in the IRCCNT5 counter                                                        |

| PLI_IKC2  | 0 idle write, the state of the counter is not modified                                                                                      |

|           | data transferred to the counter (subsequent writing 0 is not required)                                                                      |

| RSRV      | reserved (to ensure forward compatibility it is recommended to write 0)                                                                     |

| 10111     | 10001104 (to choare for ward companionity it is recommended to write 0)                                                                     |

**Note:** The functions controlled by the STR\_IRCx bits can alternatively be controlled using the SSICtrlReg register described in the chapter dedicated to the description of the SSI interface registers.

## 7.5 Register IRCCNTEnReg [WR]

This register is intended to start and stop counters, or to enable resetting by an external signal.

| D7   | D6   | D5     | D4     | D3     | D2     | D1     | D0     |

|------|------|--------|--------|--------|--------|--------|--------|

| RSRV | RSRV | EN_AB5 | EN_AB4 | EN_AB3 | EN_AB2 | EN_AB1 | EN_AB0 |

| D15  | D14  | D13    | D12    | D11    | D10    | D9     | D8     |

| RSRV | RSRV | RSRV   | RSRV   | RSRV   | RSRV   | RSRV   | RSRV   |

| D23  | D22  | D21    | D20    | D19    | D18    | D17    | D16    |

| RSRV | RSRV | EN_R5  | EN_R4  | EN_R3  | EN_R2  | EN_R1  | EN_R0  |

| D31  | D30  | D29    | D28    | D27    | D26    | D25    | D24    |

| RSRV | RSRV | RSRV   | RSRV   | RSRV   | RSRV   | RSRV   | RSRV   |

| EN_AB0 | enables IRCCNT0 counting                                                              |

|--------|---------------------------------------------------------------------------------------|

|        | 0 the counter is stopped                                                              |

|        | 1 the counter processes signals IRCCNT0_A and IRCCNT0_B                               |

| EN_AB1 | enables IRCCNT1 counting                                                              |

|        | 0 the counter is stopped                                                              |

|        | 1 the counter processes signals IRCCNT1_A and IRCCNT1_B                               |

| EN_AB2 | enables IRCCNT2 counting                                                              |

|        | 0 the counter is stopped                                                              |

|        | 1 the counter processes signals IRCCNT2_A and IRCCNT2_B                               |

| EN_AB3 | enables IRCCNT3 counting                                                              |

|        | 0 the counter is stopped                                                              |

|        | 1 the counter processes signals IRCCNT3_A and IRCCNT3_B                               |

| EN_AB4 | enables IRCCNT4 counting                                                              |

|        | 0 the counter is stopped                                                              |

|        | 1 the counter processes signals IRCCNT4_A and IRCCNT4_B                               |

| EN_AB5 | enables IRCCNT5 counting                                                              |

|        | 0 the counter is stopped                                                              |

|        | 1 the counter processes signals IRCCNT5_A and IRCCNT5_B                               |

| EN_R0  | enables IRCCNT0 setting to zero value                                                 |

|        | 0 the counter ignores IRCCNTO_R signal                                                |

|        | the counter processes signal IRCCNT0_R (active level is configurable by IRCCNT0CWReg) |

| EN_R1  | enables IRCCNT1 setting to zero value                                                 |

|        | 0 the counter ignores IRCCNT1_R signal                                                |

|        | the counter processes signal IRCCNT1_R (active level is configurable by IRCCNT1CWReg) |

| EN_R2  | enables IRCCNT0 setting to zero value                                                 |

|        | 0 the counter ignores IRCCNT2_R signal                                                |

|        | the counter processes signal IRCCNT2_R (active level is configurable by IRCCNT2CWReg) |

| EN_R3  | enables IRCCNT3 setting to zero value                                                 |

|        | 0 the counter ignores IRCCNT3_R signal                                                |

|        | the counter processes signal IRCCNT3_R (active level is configurable by IRCCNT3CWReg) |

| EN_R4  | enables IRCCNT0 setting to zero value                                                 |

|        | 0 the counter ignores IRCCNT4_R signal                                                |

|        | the counter processes signal IRCCNT4_R (active level is configurable by IRCCNT4CWReg) |

| EN_R5  | enables IRCCNT5 setting to zero value                                                 |

|        | the counter ignores IRCCNT5_R signal                                                  |

|        | the counter processes signal IRCCNT5_R (active level is configurable by IRCCNT5CWReg) |

| RSRV   | reserved (to ensure forward compatibility it is recommended to write 0)               |

## 7.6 Register IRCCNT0SetReg [WR]

This register works as a 32-bit buffer data register for writing data to the IRCCNT0 counter; data is transferred to the IRCCNT0 counter using the IRCNCNTCtrReg register.

If a incorrect value outside the range 0÷IRCCNT0RngReg is written to the IRCCNT0 counter, the counter operates in the full 32-bit range until the counter value enters the selected range 0÷IRCCNT0RngReg.

**Note:** Functionally identical registers are implemented for counters IRCCNT1 to IRCCNT5.

## 7.7 Register IRCCNT0RngReg [WR]

This 32-bit register is intended to setting the counting range of the IRCCNT0 counter, valid values are 1 to 4,294,967,295 (i.e. the full range of 32-bit values) and the IRCCNT0 counter operates in the range 0÷IRCCNT0RngReg.

If such a value is written to IRCCNT0RngReg that the current state of the IRCCNT0 counter is outside the range 0÷IRCCNT0RngReg, the counter operates in the full 32-bit range until the counter value enters the selected range 0÷IRCCNT0RngReg (by processing input signals or programming a value).

**Note:** Functionally identical registers are implemented for counters IRCCNT1 to IRCCNT5.

## 7.8 Register IRCCNT0StrReg [RD]

This register works as a 32-bit buffer data register for software reading of IRCCNT0 counter. Current counter value is stored into IRCCNT0StrReg capture register using the IRCNCNTCtrlReg register.

**Note:** Functionally identical registers are implemented for counters IRCCNT1 to IRCCNT5.

## 7.9 Register IRCCNT0CWReg [WR]

This register is intended to configuring the IRCCNT0 counter.

| D31÷D8  | D7   | D6   | D5 | D4 | D3  | D2   | D1  | D0    |

|---------|------|------|----|----|-----|------|-----|-------|

| RSRV-32 | RSRV | MODE |    |    | ERR | RSRV | LPF | R_CFG |

R CFG configuration of the active IRCCNTO R signal level the counter is set to zero value by the L level of the input signal the counter is set to zero value by the H level of the input signal **LPF** turning on/off the low-pass filter of the encoder input signals filter is inactive 1 filter is activated **ERR** resetting the ERR flag in IRCCNT0StatReg 0 idle write, flag status remains without change the flag is reset (subsequent writing 0 is not required) 1 MODE configuration of the counter operating mode (described in detail in the User's Guide) quadrature mode X1 000 001 quadrature mode X2 010 quadrature mode X4 011 reserved "up/down" mode 100 "count/dir" mode 101 110 "count/gate" mode reserved 111 **RSRV** reserved (to ensure forward compatibility it is recommended to write 0) RSRV-32 reserved (to ensure forward compatibility it is recommended to write 0) although only eight bits of register are significant, it is necessary to access the register with 32-bit data

**Note:** Functionally identical registers are implemented for counters IRCCNT1 to IRCCNT5.

## 7.10 Register IRCCNT0StatReg [RD]

This register is intended to read the status flags of the IRCCNT0 counter.

| D31÷D8  | D7   | D6   | D5   | D4   | D3  | D2        | D1        | DO        |

|---------|------|------|------|------|-----|-----------|-----------|-----------|

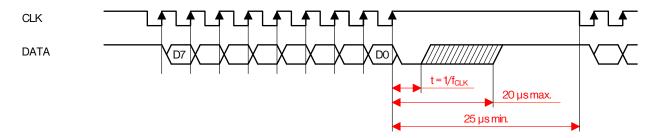

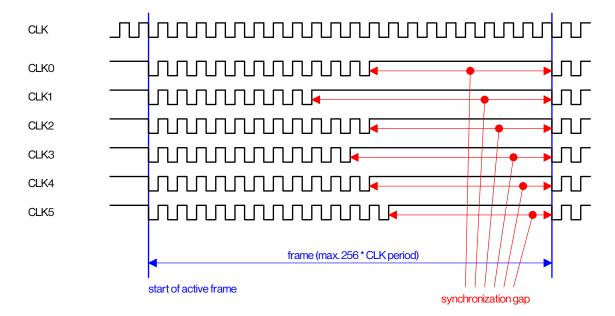

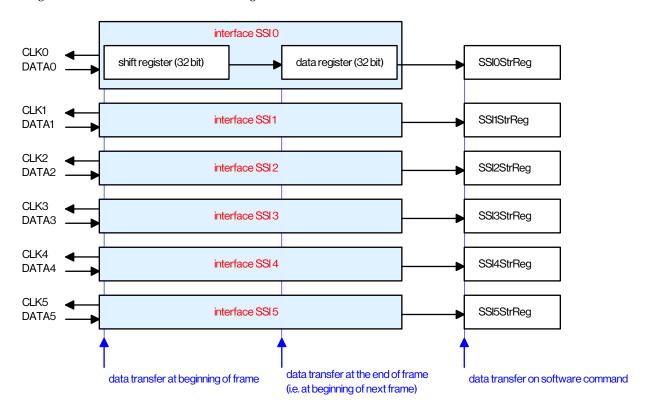

| RSRV-32 | RSRV | RSRV | RSRV | RSRV | ERR | IRCCNT0_R | IRCCNT0_B | IRCCNT0_A |